LM4550 AC '97 Rev 2.1 Multi-Channel Audio Codec with Stereo Headphone

Amplifier, Sample Rate Conversion and National 3D Sound

Literature Number: SNAS032E

OBSOLETE September 23, 2011

### AC '97 Rev 2.1 Multi-Channel Audio Codec with Stereo Headphone Amplifier, Sample Rate Conversion and National 3D Sound

### **General Description**

The LM4550 is an audio codec for PC systems which is fully PC99 compliant and performs the analog intensive functions of the AC '97 Rev 2.1 architecture. Using 18-bit Sigma-Delta ADCs and DACs, the LM4550 provides 90 dB of Dynamic Range.

The LM4550 was designed specifically to provide a high guality audio path and provide all analog functionality in a PC audio system. It features full duplex stereo ADCs and DACs and analog mixers with access to 4 stereo and 4 mono inputs. Each mixer input has separate gain, attenuation and mute control and the mixers drive 1 mono and 2 stereo outputs. each with attenuation and mute control. The LM4550 provides a stereo headphone amplifier as one of its stereo outputs and also supports National's 3D Sound stereo enhancement and a comprehensive sample rate conversion capability. The sample rate for the ADCs and DACs can be programmed separately with a resolution of 1 Hz to convert any rate in the range 4 kHz - 48 kHz. Sample timing from the ADCs and sample request timing for the DACs are completely deterministic to ease task scheduling and application software development. These features together with an extended temperature range also make the LM4550 suitable for non-PC codec applications.

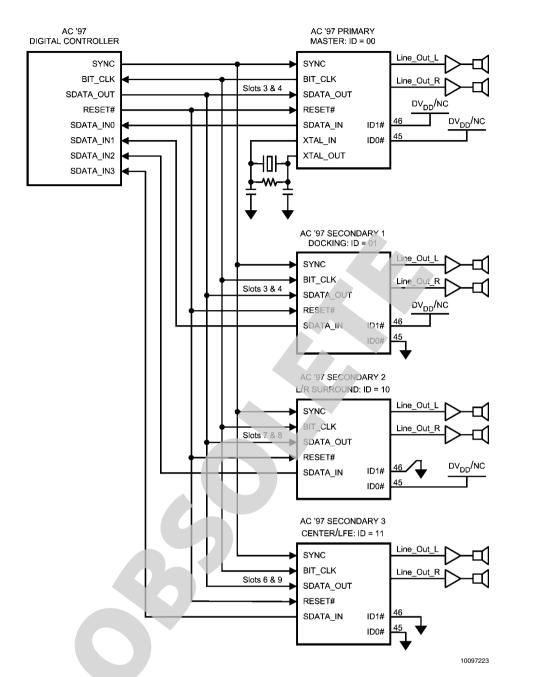

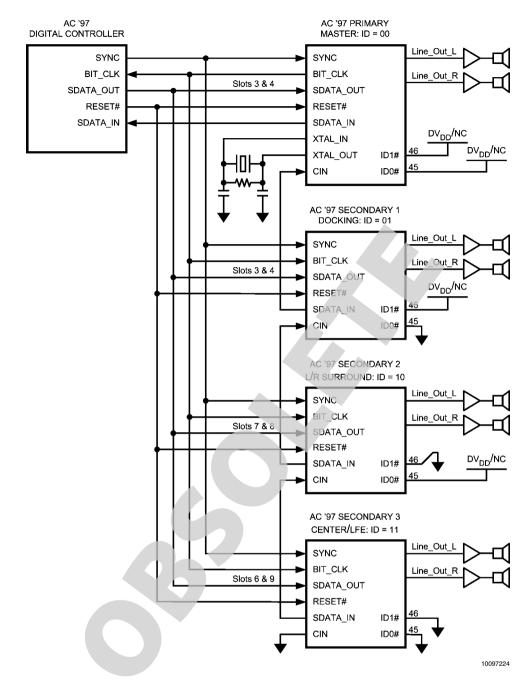

The LM4550 features the ability to connect several codecs together in a system to provide up to 6 simultaneous channels of streaming data on Output Frames (Controller to Codec) for surround sound applications. Such systems can also support up to 8 simultaneous channels of streaming data on Input Frames (Codec to Controller). Multiple codec systems can be built either using the standard AC Link configuration (*i.e.* of one serial data signal to the Controller per codec) or using a unique National Semiconductor feature for chaining codecs together. This chain feature shares only a single data signal to the controller among multiple codecs.

The AC '97 architecture separates the analog and digital functions of the PC audio system allowing both for system design flexibility and increased performance.

### **Key Specifications**

- Analog Mixer Dynamic Range

- DAC Dynamic RangeADC Dynamic Range

89 dB (typ) 90 dB (typ) 0.02% (typ) into

97 dB (typ)

32Ω

Headphone Amp THD+N at 50 mW

### **Features**

- AC '97 Rev 2.1 compliant

- High quality Sample Rate Conversion from 4 kHz to 48 kHz in 1 Hz increments

- Supports up to 6 DAC channel systems with multiple LM4550s or with other National LM45xx codecs

- Unique National chaining function shares a single controller SDATA\_IN pin among multiple codecs

- Stereo headphone amp with separate gain control

- National's 3D Sound stereo enhancement circuitry

Advanced power management support

- External Amplifier Power Down (EAPD) control

- PC Beep passthrough to Line Out during Initialization or Cold Reset

- Digital 3.3V and 5V supply options

- Extended Temperature: -40°C ≤ T<sub>A</sub> ≤ 85°C

### **Applications**

- Desktop PC audio systems on PCI cards, AMR cards, or with motherboard chips sets featuring AC Link

- Portable PC systems as on MDC cards, or with a chipset or accelerator featuring AC Link

- General Audio Frequency Systems requiring 2, 4 or 6 DAC channels and/or up to 8 ADC channels

© 2011 National Semiconductor Corporation 100972

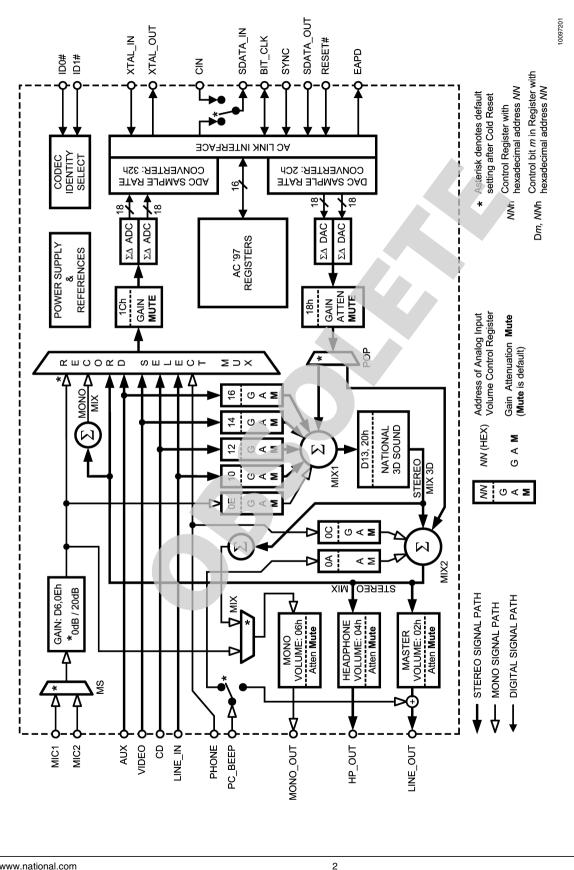

### **Block Diagram**

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage              | 6.0V                           |

|-----------------------------|--------------------------------|

| Storage Temperature         | –65°C to +150°C                |

| Input Voltage               | -0.3V to V <sub>DD</sub> +0.3V |

| ESD Susceptibility (Note 2) | 2000V                          |

| pin 3                       | 750V                           |

| ESD Susceptibility (Note 3) | 200V                           |

| pin 3                       | 100V                           |

| Junction Temperature        | 150°C                          |

### **Operating Ratings**

#### Temperature Range

| T <sub>MIN</sub> ≤ T <sub>A</sub> ≤ T <sub>MAX</sub> ( <i>Note 4</i> ) | $-40^{\circ}C \le T_A \le 85^{\circ}C$ |

|------------------------------------------------------------------------|----------------------------------------|

| Analog Supply Range                                                    | $4.2V \le AV_{DD} \le 5.5V$            |

| Digital Supply Range                                                   | $3.0V \le DV_{DD} \le 5.5V$            |

**Electrical Characteristics** (*Note 1, Note 5*) The following specifications apply for  $AV_{DD} = 5V$ ,  $DV_{DD} = 5V$ , Fs = 48 kHz, single codec configuration, unless otherwise noted. Limits apply for  $T_A = 25^{\circ}$ C. The reference for 0 dB is 1 Vrms unless otherwise specified.

|                  |                                          |                                                                                    | LM4                          | 1550                       | Unite             |

|------------------|------------------------------------------|------------------------------------------------------------------------------------|------------------------------|----------------------------|-------------------|

| Symbol           | Parameter                                | Conditions                                                                         | Typical<br>( <i>Note 6</i> ) | Limit<br>( <i>Note 7</i> ) | Units<br>(Limits) |

| AV <sub>DD</sub> | Analog Supply Range                      |                                                                                    |                              | 4.2                        | V (min)           |

|                  |                                          |                                                                                    |                              | 5.5                        | V (max)           |

| DV <sub>DD</sub> | Digital Supply Range                     |                                                                                    |                              | 3.0                        | V (min)           |

|                  |                                          |                                                                                    |                              | 5.5                        | V (max)           |

| D <sub>IDD</sub> | Digital Quiescent Power Supply           | DV <sub>DD</sub> = 5 V                                                             | 43                           |                            | mA                |

|                  | Current                                  | DV <sub>DD</sub> = 3.3 V                                                           | 20                           |                            | mA                |

| A <sub>IDD</sub> | Analog Quiescent Power Supply<br>Current |                                                                                    | 53                           |                            | mA                |

| I <sub>DSD</sub> | Digital Shutdown Current                 |                                                                                    | 500                          |                            | μA                |

| I <sub>ASD</sub> | Analog Shutdown Current                  |                                                                                    | 30                           |                            | μA                |

| V <sub>REF</sub> | Reference Voltage                        |                                                                                    | 2.23                         |                            | V                 |

| PSRR             | Power Supply Rejection Ratio             |                                                                                    | 40                           |                            | dB                |

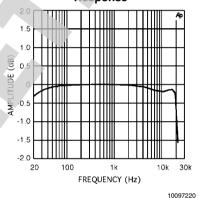

| Analog Loop      | othrough Mode ( <i>Note 8</i> )          |                                                                                    |                              |                            | •                 |

|                  | Dynamic Range (Note 9)                   | CD Input to Line Output, -60 dB Input THD<br>+N, A-Weighted                        | 97                           | 90                         | dB (min)          |

| THD              | Total Harmonic Distortion                | $V_0 = -3 \text{ dB}, \text{ f} = 1 \text{ kHz}, \text{ R}_L = 10 \text{ k}\Omega$ | 0.01                         | 0.02                       | % (max)           |

| Analog Input     | t Section                                |                                                                                    |                              |                            |                   |

| V <sub>IN</sub>  | Line Input Voltage                       | LINE_IN, AUX, CD, VIDEO, PC_BEEP, PHONE                                            | 1                            |                            | Vrms              |

| V <sub>IN</sub>  | Mic Input with 20 dB Gain                |                                                                                    | 0.1                          |                            | Vrms              |

| V <sub>IN</sub>  | Mic Input with 0 dB Gain                 |                                                                                    | 1                            |                            | Vrms              |

| Xtalk            | Crosstalk                                | CD Left to Right                                                                   | -95                          |                            | dB                |

| Z <sub>IN</sub>  | Input Impedance ( <i>Note 9</i> )        | All Analog Inputs                                                                  | 40                           | 10                         | kΩ (min)          |

| C <sub>IN</sub>  | Input Capacitance                        |                                                                                    | 15                           |                            | pF                |

|                  | Interchannel Gain Mismatch               | CD Left to Right                                                                   | 0.01                         |                            | dB                |

| Record Gain      | Amplifier - ADC                          | •                                                                                  |                              |                            |                   |

| A <sub>S</sub>   | Step Size                                | 0 dB to 22.5 dB                                                                    | 1.5                          |                            | dB                |

| A <sub>M</sub>   | Mute Attenuation (Note 9)                |                                                                                    | 86                           |                            | dB                |

| Mixer Sectio     | n                                        |                                                                                    |                              |                            |                   |

| A <sub>S</sub>   | Step Size                                | +12 dB to -34.5 dB                                                                 | 1.5                          |                            | dB                |

| A <sub>M</sub>   | Mute Attenuation                         |                                                                                    | 86                           |                            | dB                |

|                      |                                    |                                                                                         | LM4                          | 550                        | Units    |

|----------------------|------------------------------------|-----------------------------------------------------------------------------------------|------------------------------|----------------------------|----------|

| Symbol               | Parameter                          | Conditions                                                                              | Typical<br>( <i>Note 6</i> ) | Limit<br>( <i>Note 7</i> ) | (Limits) |

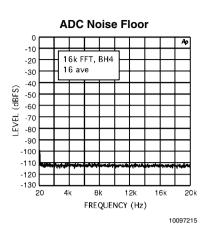

| Analog to Di         | gital Converters                   | •                                                                                       |                              |                            |          |

|                      | Resolution                         |                                                                                         | 18                           |                            | Bits     |

|                      | Dynamic Range ( <i>Note 9</i> )    | -60 dB Input THD+N, A-Weighted                                                          | 90                           | 86                         | dB (min  |

|                      | Frequency Response                 | -1 dB Bandwidth                                                                         | 20                           |                            | kHz      |

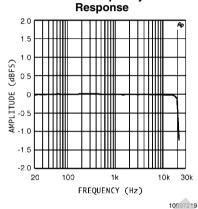

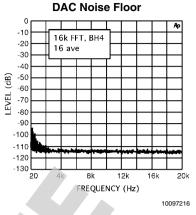

| Digital to An        | alog Converters                    |                                                                                         |                              |                            | -        |

|                      | Resolution                         |                                                                                         | 18                           |                            | Bits     |

|                      | Dynamic Range ( <i>Note 9</i> )    | -60 dB Input THD+N, A-Weighted                                                          | 89                           | 85                         | dB (min  |

| THD                  | Total Harmonic Distortion          | $V_{IN} = -3 \text{ dB}, \text{ f} = 1 \text{ kHz}, \text{ R}_{L} = 10 \text{ k}\Omega$ | 0.01                         |                            | %        |

|                      | Frequency Response                 |                                                                                         | 20 - 21 k                    |                            | Hz       |

|                      | Group Delay (Note 9)               |                                                                                         |                              | 2                          | ms (max  |

|                      | Out of Band Energy (Note 10)       |                                                                                         | -40                          |                            | dB       |

|                      | Stop Band Rejection                |                                                                                         | 70                           |                            | dB       |

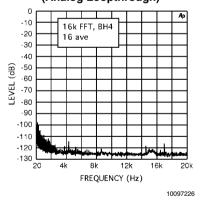

| D <sub>T</sub>       | Discrete Tones                     |                                                                                         | -96                          |                            | dB       |

| Analog Outp          | ut Section                         |                                                                                         |                              |                            |          |

| A <sub>S</sub>       | Step Size                          | 0 dB to -46.5 dB                                                                        | 1.5                          |                            | dB       |

| A <sub>M</sub>       | Mute Attenuation                   |                                                                                         | 86                           |                            | dB       |

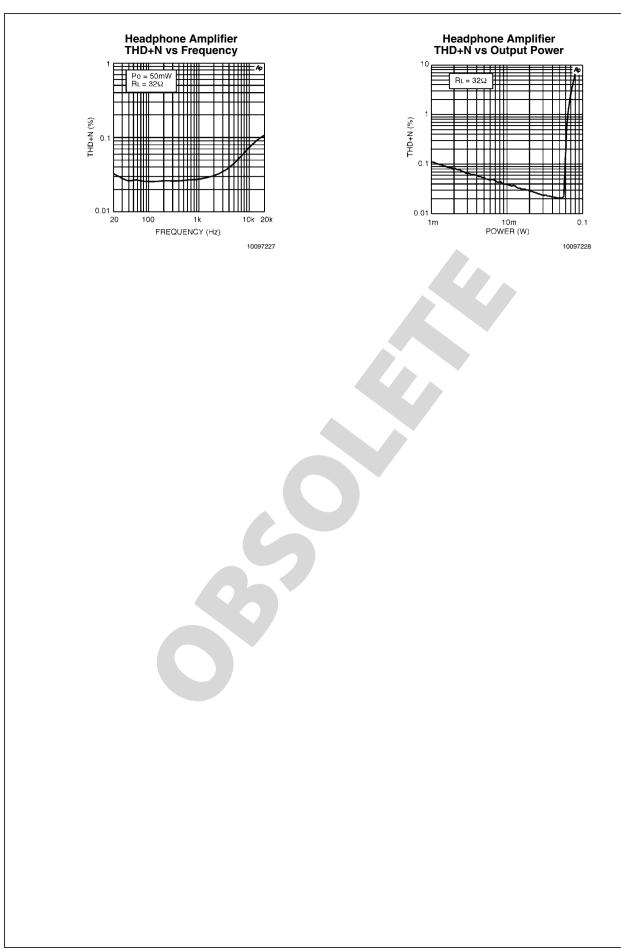

|                      | Headphone Amplifier Total Harmonic | Loopthrough Mode ( <i>Note 8</i> ), $R_L = 32 \Omega$ , $f =$                           |                              |                            | 1        |

| THD+N                | Distortion plus Noise              | $1 \text{ kHz}, P_{\text{out}} = 50 \text{ mW}$                                         | 0.02                         |                            | %        |

| Z <sub>OUT</sub>     | Output Impedance ( <i>Note 9</i> ) | HP_OUT_L, HP_OUT_R                                                                      | TBD                          |                            | Ω        |

|                      |                                    | LINE_OUT_L, LINE_OUT_R,                                                                 |                              |                            |          |

| Z <sub>OUT</sub>     | Output Impedance (Note 9)          | MONO_OUT                                                                                | TBD                          |                            | Ω        |

| Digital I/O (N       | lote 9)                            |                                                                                         |                              |                            |          |

| V <sub>IH</sub>      | High level input voltage           |                                                                                         |                              | 0.40 x<br>DV <sub>DD</sub> | V (min)  |

| V <sub>IL</sub>      | Low level input voltage            |                                                                                         |                              | 0.30 x<br>DV <sub>DD</sub> | V (max   |

| V <sub>OH</sub>      | High level output voltage          |                                                                                         |                              | 0.50 x<br>DV <sub>DD</sub> | V (min)  |

| V <sub>OL</sub>      | Low level output voltage           |                                                                                         |                              | 0.20 x<br>DV <sub>DD</sub> | V (max   |

| l                    | Input Leakage Current              | AC Link inputs                                                                          |                              | ±10                        | μA       |

| <br>I_               | Tri state Leakage Current          | High impedance AC Link outputs                                                          |                              | ±10                        | μΑ       |

| I <sub>DR</sub>      | Output drive current               | AC Link outputs                                                                         | 5                            |                            | mA       |

|                      | g Specifications ( <i>Note 9</i> ) | ·                                                                                       |                              |                            |          |

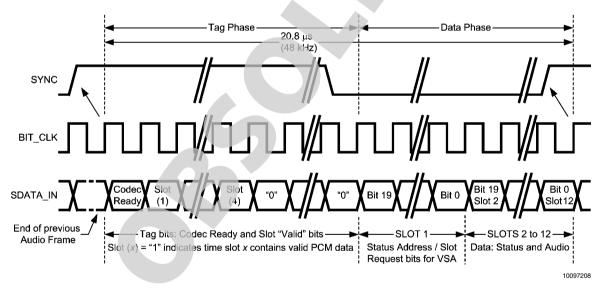

| F <sub>BC</sub>      | BIT_CLK frequency                  |                                                                                         | 12.288                       |                            | MHz      |

| T <sub>BCP</sub>     | BIT_CLK period                     |                                                                                         | 81.4                         |                            | ns       |

| т <sub>сн</sub>      | BIT_CLK high                       | Variation of BIT_CLK duty cycle from 50%                                                |                              | ±20                        | % (max   |

| F <sub>SYNC</sub>    | SYNC frequency                     |                                                                                         | 48                           |                            | kHz      |

|                      | SYNC period                        |                                                                                         | 20.8                         |                            |          |

| Т <sub>SP</sub><br>т |                                    |                                                                                         | 1.3                          |                            | μs       |

| Т <sub>SH</sub><br>т | SYNC high pulse width              |                                                                                         |                              |                            | μs       |

| T <sub>SL</sub>      | SYNC low pulse width               |                                                                                         | 19.5                         |                            | µs       |

| T <sub>DSETUP</sub>  | Setup Time for codec data input    | SDATA_OUT to falling edge of BIT_CLK                                                    |                              | 15                         | ns (min  |

| T <sub>DHOLD</sub>   | Hold Time for codec data input     | Hold time of SDATA_OUT from falling edge<br>of BIT_CLK                                  |                              | 5                          | ns (min  |

| T <sub>SSETUP</sub>  | Setup Time for codec SYNC input    | SYNC to rising edge of BIT_CLK                                                          |                              | TBD                        | ns (min  |

| T <sub>SHOLD</sub>   | Hold Time for codec SYNC input     | Hold time of SYNC from rising edge of<br>BIT_CLK                                        |                              | TBD                        | ns (min  |

|                         |                                     |                                                                  | LM4                          | 1550                       |                   |

|-------------------------|-------------------------------------|------------------------------------------------------------------|------------------------------|----------------------------|-------------------|

| Symbol                  | Parameter                           | Conditions                                                       | Typical<br>( <i>Note 6</i> ) | Limit<br>( <i>Note 7</i> ) | Units<br>(Limits) |

| т <sub>со</sub>         | Output Valid Delay                  | Output Delay of SDATA_IN from rising edge of BIT_CLK             | IN from rising TBD           |                            | ns (max)          |

| T <sub>RISE</sub>       | Rise Time                           | BIT_CLK, SYNC, SDATA_IN or<br>SDATA_OUT                          |                              | 6                          | ns (max)          |

| T <sub>FALL</sub>       | Fall Time                           | BIT_CLK, SYNC, SDATA_IN or<br>SDATA_OUT                          |                              | 6                          | ns (max)          |

| T <sub>CS</sub>         | Chain Propagation Delay             | Data Delay from CIN to SDATA_IN when the chain feature is active | TBD                          | TBD                        | ns (max)          |

| T <sub>RST_LOW</sub>    | RESET# active low pulse width       | For Cold Reset                                                   |                              | 1.0                        | µs (min)          |

| T <sub>RST2CLK</sub>    | RESET# inactive to BIT_CLK start up | For Cold Reset                                                   | TBD                          | 162.8                      | ns (min)          |

| Т <sub>SH</sub>         | SYNC active high pulse width        | For Warm Reset                                                   | 1.3                          | TBD                        | µs (min)          |

| T <sub>SYNC2CLK</sub>   | SYNC inactive to BIT_CLK start up   | For Warm Reset                                                   | TBD                          | 162.8                      | ns (min)          |

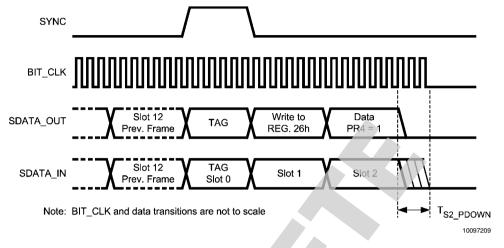

| T <sub>S2_PDOWN</sub>   | AC Link Power Down Delay            | Delay from end of Slot 2 to BIT_CLK,<br>SDATA_IN low             |                              | 1                          | µs (max)          |

| T <sub>SUPPLY2RST</sub> | Power On Reset                      | Time from minimum valid supply levels to end of Reset            |                              | 1                          | µs (min)          |

| T <sub>SU2RST</sub>     | Setup to trailing edge of RESET#    | For ATE Test Mode                                                |                              | 15                         | ns (min)          |

| T <sub>RST2HZ</sub>     | Rising edge of RESET# to Hi-Z       | For ATE Test Mode                                                |                              | 25                         | ns (max)          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 2: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 3: Machine Model, 220 pF - 240 pF discharged through all pins.

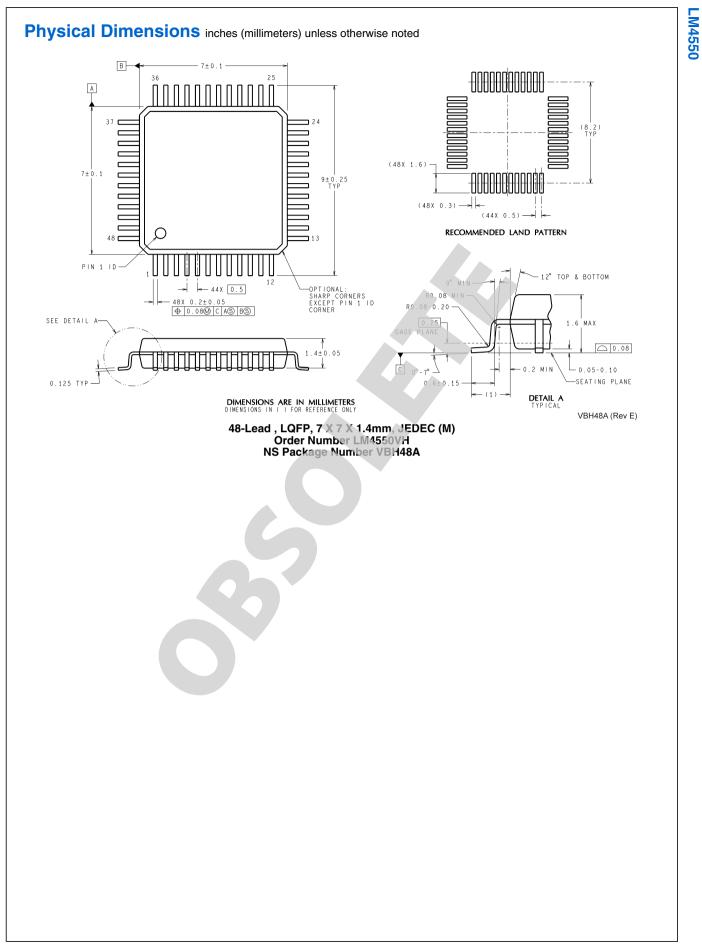

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4550,  $T_{JMAX} = 150^{\circ}$ C. The typical junction-to-ambient thermal resistance is 74°C/W for package number VBH48A.

Note 5: All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Loopthrough Mode describes a path from an analog input through the analog mixers to an analog output.

Note 9: These specifications are guaranteed by design and characterization; they are not production tested.

Note 10: Out of band energy is measured from 28.8 kHz to 100 kHz relative to a 1 Vrms DAC output.

LM455(

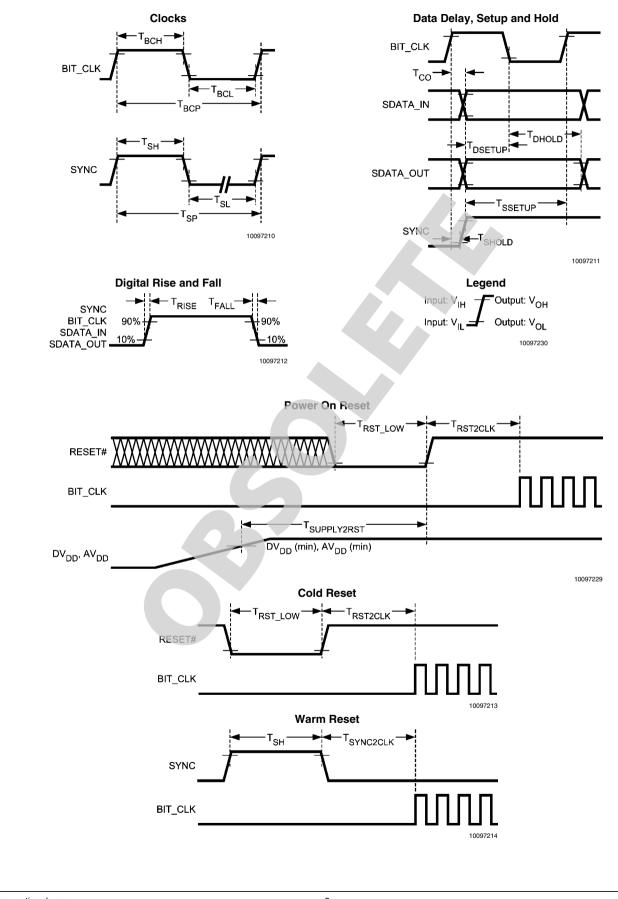

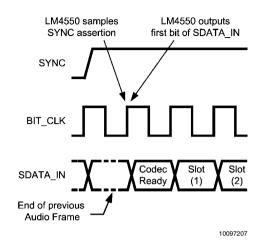

### **Timing Diagrams**

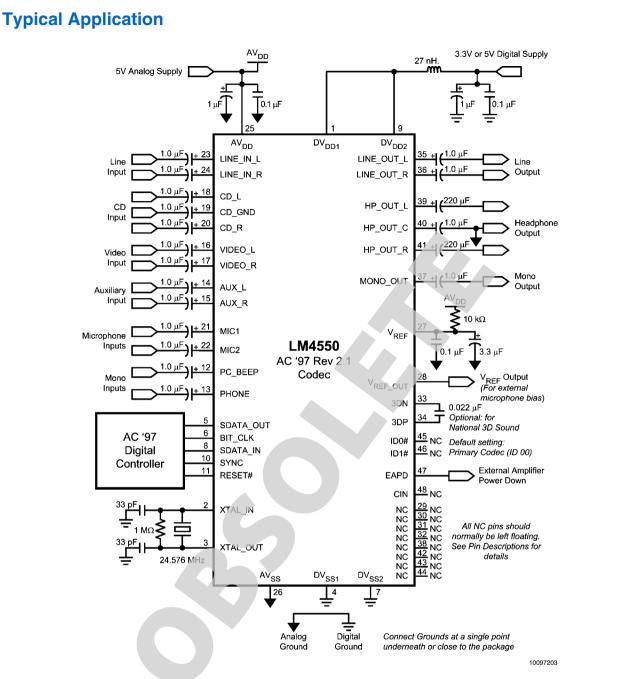

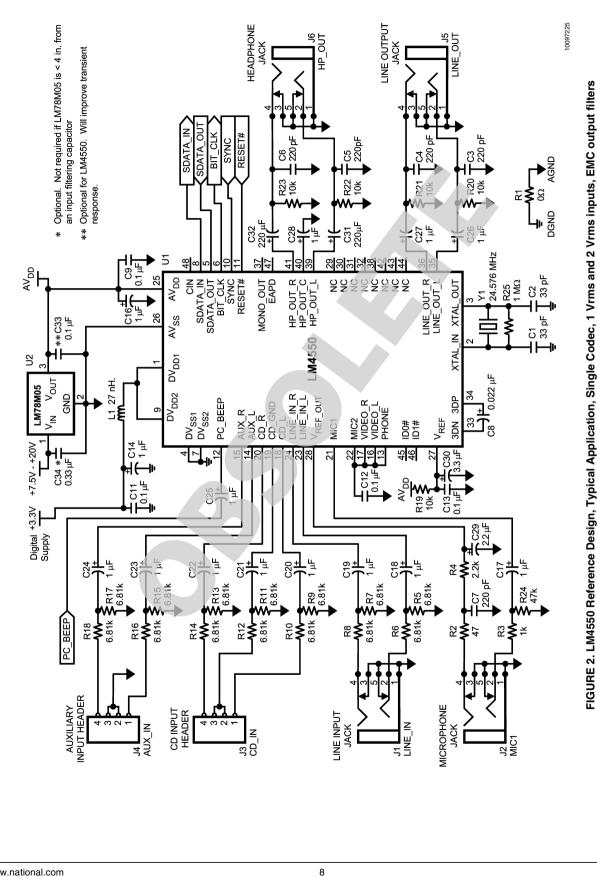

FIGURE 1. LM4550 Typical Application Circuit, Single Codec, 1 Vrms inputs

#### **APPLICATION HINTS**

- The LM4550 must be initialized by using RESET# to perform a Power On Reset as shown in the Power On Reset Timing Diagram

- $V_{\text{REF}}$  must be pulled high to  $\text{AV}_{\text{DD}}$  with a 10 k $\Omega$  resistor to ensure correct operation

- Don't leave unused inputs floating. Tie all unused inputs together and connect to Analog Ground through a capacitor (e.g. 0.1 μF)

- Do not leave CD\_GND floating when using the CD stereo input. CD\_GND is the AC signal reference for the CD channels and ٠ should be connected to the CD source ground (Analog Ground may also be acceptable) through a 1 µF capacitor

- If using a non-standard AC Link controller take care to keep the SYNC and SDATA OUT signals low during Cold Reset to avoid accidentally activating the ATE or Vendor test modes

- The PC\_Beep input should be explicitly muted if not used since it defaults to 0 dB gain on reset, unlike the mute default of the • other analog inputs

LM4550

www.national.com

100972 Version 6 Revision 3 Print Date/Time: 2011/09/23 10:22:49

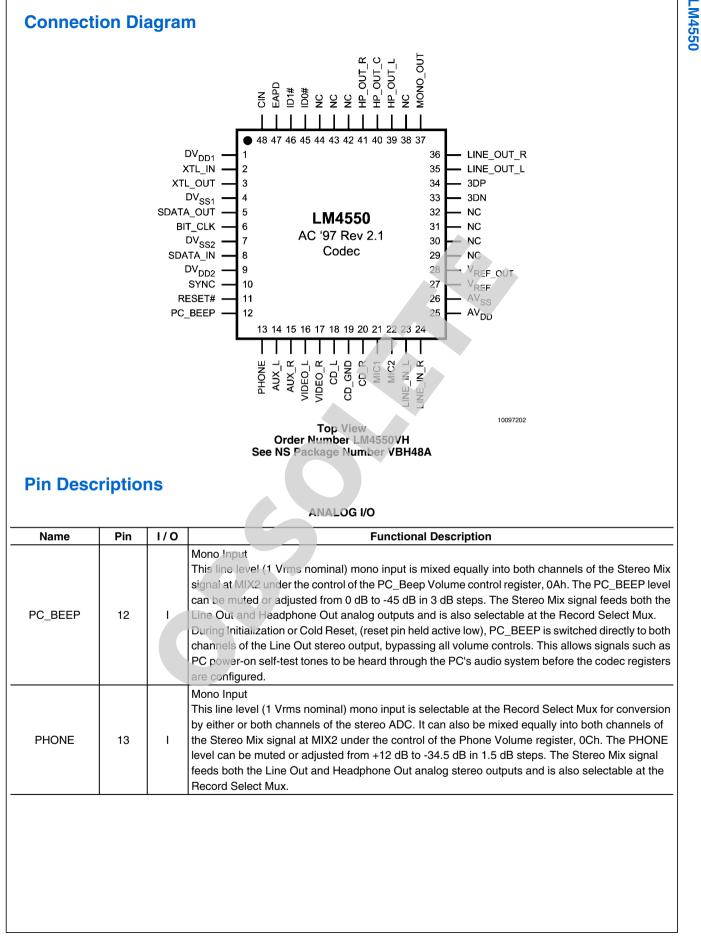

| Name    | Pin | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUX_L   | 14  | I   | Left Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the left channel of the stereo Record Select<br>Mux for conversion by the left channel ADC. It can also be mixed into the left channel of the Stereo<br>Mix 3D signal at MIX1 under the control of the Aux Volume register, 16h. The AUX_L level can be<br>muted (along with AUX_R) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix 3D is<br>combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and<br>Headphone Out.                                |

| AUX_R   | 15  | I   | Right Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the right channel of the stereo Record Select<br>Mux for conversion by the right channel ADC. It can also be mixed into the right channel of the<br>Stereo Mix 3D signal at MIX1 under the control of the Aux Volume register, 16h. The AUX_R level<br>can be muted (along with AUX_L) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix<br>3D is combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and<br>Headphone Out.                            |

| VIDEO_L | 16  | I   | Left Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the left channel of the stereo Record Select<br>Mux for conversion by the left channel ADC. It can also be mixed into the left channel of the Stereo<br>Mix 3D signal at MIX1 under the control of the Video Volume register, 14h. The VIDEO_L level can<br>be muted (along with VIDEO_R) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix<br>3D is combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and<br>Headphone Out.                          |

| VIDEO_R | 17  | I   | Right Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the right channel of the stereo Record Select<br>Mux for conversion by the right channel ADC. It can also be mixed into the right channel of the<br>Stereo Mix 3D signal at MIX1 under the control of the Video Volume register, 14h. The VIDEO_R<br>level can be muted (along with VIDEO_L) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps.<br>Stereo Mix 3D is combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line<br>Out and Headphone Out.                      |

| CD_L    | 18  | I   | Left Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the left channel of the stereo Input Mux for<br>conversion by the left channel ADC. It can also be mixed into the left channel of the Stereo Mix 3D<br>signal at MIX1 under the control of the CD Volume register, 12h. The CD_L level can be muted<br>(along with CD_R) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix 3D is mixed<br>into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and Headphone Out.                                                 |

| CD_GND  | 19  | I   | AC Ground Reference<br>This input is the reference for the signals on both CD_L and CD_R. CD_GND is NOT a DC ground<br>and must be AC-coupled to the stereo source ground common to both CD_L and CD_R. The three<br>inputs CD_GND, CD_L and CD_R act together as a quasi-differential stereo input with CD_GND<br>providing AC common-mode feedback to reject ground noise. This can improve the input SNR for<br>a stereo source with a good common ground but precision resistors may be needed in any external<br>attenuators to achieve the necessary balance between the two channels. |

| CD_R    | 20  | I   | Right Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the right channel of the stereo Input Mux for<br>conversion by the right channel ADC. It can also be mixed into the right channel of the Stereo Mix<br>3D signal at MIX1 under the control of the CD Volume register, 12h. The CD_R level can be muted<br>(along with CD_L) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix 3D is combined<br>into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and Headphone Out.                                          |

٦

| Name       | Pin | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIC1       | 21  | I   | Mono microphone input<br>Either MIC1 or MIC2 can be muxed to a programmable boost amplifier with selection by the MS<br>bit (bit D8) in the General Purpose register, 20h. The boost amplifier gain (0 dB or 20 dB) is set by<br>the 20dB bit (D6) in the Mic Volume register, 0Eh. Nominal input levels at the two gain settings are<br>1 Vrms and 0.1 Vrms respectively. The amplifier output is selectable (Record Select register, 1Ah)<br>by either the right or left channels of the Record Select Mux for conversion on either or both<br>channels of the stereo ADC. The amplifier output can also be accessed at the stereo mixer MIX1<br>(muting and mixing adjustments via Mic Volume register, 0Eh) where it is mixed equally into both<br>left and right channels of Stereo Mix 3D for access to the stereo outputs Line Out and Headphone<br>Out. Access to the Mono analog output is selected by a mux controlled by the MIX bit (D9) in<br>General Purpose register, 20h. |

| MIC2       | 22  | I   | Mono microphone input<br>Either MIC1 or MIC2 can be muxed to a programmable boost amplifier with selection by the MS<br>bit (bit D8) in the General Purpose register, 20h. The boost amplifier gain (0 dB or 20 dB) is set by<br>the 20dB bit (D6) in the Mic Volume register, 0Eh. Nominal input levels at the two gain settings are<br>1 Vrms and 0.1 Vrms respectively. The amplifier output is selectable (Record Select register, 1Ah)<br>by either the right or left channels of the Record Select Mux for conversion on either or both<br>channels of the stereo ADC. The amplifier output can also be accessed at the stereo mixer MIX1<br>(muting and mixing adjustments via Mic Volume register, 0En) where it is mixed equally into both<br>left and right channels of Stereo Mix 3D for access to the stereo outputs Line Out and Headphone<br>Out. Access to the Mono analog output is selected by a mux controlled by the MIX bit (D9) in<br>General Purpose register, 20h. |

| LINE_IN_L  | 23  | I   | Left Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the left channel of the stereo Record Select<br>Mux for conversion by the left channel ADC. It can also be mixed into the left channel of the Stereo<br>Mix 3D signal at MIX1 under the control of the Line In Volume register, 10h. The LINE_IN_L level<br>can be muted (along with LINE_IN_R) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo<br>Mix 3D is combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out<br>and Headphone Out.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LINE_IN_R  | 24  | I   | Right Stereo Channel Input<br>This line level input (1 Vrms nominal) is selectable at the right channel of the stereo Input Mux for<br>conversion by the right channel ADC. It can also be mixed into the right channel of the Stereo Mix<br>3D signal at MIX1 under the control of the Line In Volume register, 10h. The LINE_IN_R level can<br>be muted (along with LINE_IN_L) or adjusted from +12 dB to -34.5 dB in 1.5 dB steps. Stereo Mix<br>3D is combined into the Stereo Mix signal at MIX2 for access to the stereo outputs Line Out and<br>Headphone Out.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LINE_OUT_L | 35  | 0   | Left Stereo Channel Output<br>This line level output (1 Vrms nominal) is fed from the left channel of the Stereo Mix signal from<br>MIX2 via the Master Volume register, 02h. The LINE_OUT_L amplitude can be muted (along with<br>LINE_OUT_R) or adjusted from 0 dB to -46.5 dB in 1.5 dB steps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LINE_OUT_R | 36  | 0   | Right Stereo Channel Output<br>This line level output (1 Vrms nominal) is fed from the right channel of the Stereo Mix signal from<br>MIX2 via the Master Volume register, 02h. The LINE_OUT_R amplitude can be muted (along with<br>LINE_OUT_L) or adjusted from 0 dB to -46.5 dB in 1.5 dB steps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MONO_OUT   | 37  | 0   | Mono Output<br>This mono line level output (1 Vrms nominal) is fed from either a microphone input (MIC1 or MIC2,<br>after boost amplifier) or from the mono sum of the left and right Stereo Mix 3D channels from MIX1.<br>The optional National 3D Sound enhancement can be disabled (default) by the 3D bit (bit D13) in<br>the General Purpose register, 20h. Choice of input is by the MIX bit (D9) in the same register.<br>MIX=0 selects a microphone input. Output level can be muted or adjusted from 0 dB to -46.5 dB<br>in 1.5 dB steps via the Mono Volume register, 06h.                                                                                                                                                                                                                                                                                                                                                                                                      |

| HP_OUT_L   | 39  | ο   | Left Stereo Channel Output<br>This line level output (1 Vrms nominal) is fed from the left channel of the Stereo Mix signal from<br>MIX2 via the Headphone Volume register, 04h. The HP_OUT_L amplitude can be muted (along<br>with HP_OUT_R) or adjusted from 0 dB to - 46.5 dB in 1.5 dB steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Name      | Pin | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HP_OUT_C  | 40  | I   | AC Ground Reference<br>In normal use, this input is the AC ground reference for HP_OUT_L and HP_OUT_R. It must be<br>capacitively coupled to analog ground with short traces to maximize performance. It is NOT a Do<br>ground.<br>For non-stereo applications it may also be used to provide common-mode feedback with HP_OU<br>configured as one differential output rather than as outputs for two single-ended stereo channels                                                                                                                                                                                                                                                                              |

| HP_OUT_R  | 41  | o   | Right Stereo Channel Output<br>This line level output (1 Vrms nominal) is fed from the right channel of the Stereo Mix signal from<br>MIX2 via the Headphone Volume register, 04h. The HP_OUT_R amplitude can be muted (along<br>with HP_OUT_L) or adjusted from 0 dB to - 46.5 dB in 1.5 dB steps                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |     |     | DIGITAL I/O AND CLOCKING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Name      | Pin | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTL_IN    | 2   | I   | 24.576 MHz crystal or external oscillator input<br>To complete the oscillator circuit use a fundamental mode crystal operating in parallel resonance<br>and connect a 1M $\Omega$ resistor across pins 2 and 3. Choose the load capacitors ( <i>Figure 2, C1, C2</i> ) suit the load capacitance required by the crystal ( <i>e.g.</i> C1 = C2 = 33 pF for a 20 pF crystal. Assume<br>that each 'Input + trace' capacitance is 7 pF).<br>This pin may also be used as the input for an external oscillator (24.576 MHz nominal) at standar<br>logic levels (V <sub>IH</sub> , V <sub>IL</sub> ).<br>This pin is only used when the codec is in Primary mode. It may be left open (NC) for any Secondar<br>mode. |

| XTL_OUT   | 3   | 0   | 24.576 MHz crystal output<br>Used with XTAL_IN to configure a crystal oscillator.<br>When the codec is used with an external oscillator this pin should be left open (NC).<br>When the codec is configured in a Secondary mode this pin is not used and may be left open (NC)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

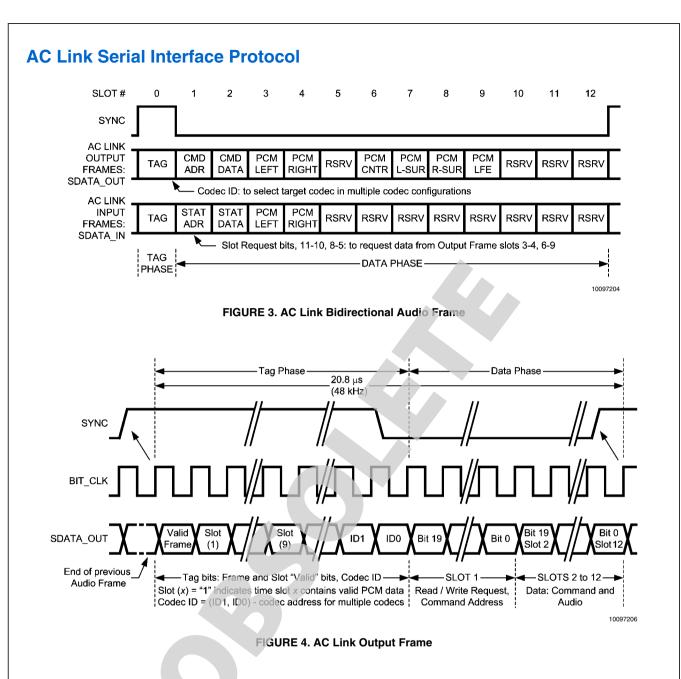

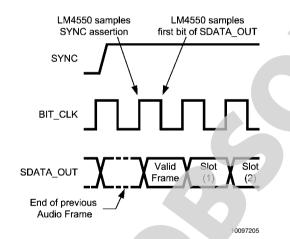

| SDATA_OUT | 5   | I   | Input to codec<br>This is the input for AC Link Output Frames from an AC '97 Digital Audio Controller to the LM455<br>codec. These frames can contain both control data and DAC PCM audio data. This input is sample<br>by the LM4550 on the falling edge of BIT_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIT_CLK   | 6   | I/O | AC Link clock<br>An OUTPUT when in Primary Codec mode. This pin provides a 12.288 MHz clock for the AC Lin<br>The clock is derived (internally divided by two) from the 24.576 MHz signal at the crystal input<br>(XTL_IN).<br>This pin is an INPUT when the codec is configured in any of the Secondary Codec modes and<br>would normally use the AC Link clock generated by a Primary Codec.                                                                                                                                                                                                                                                                                                                  |

| SDATA_IN  | 8   | 0   | Output from codec<br>This is the output for AC Link Input Frames from the LM4550 codec to an AC '97 Digital Audio<br>Controller. These frames can contain both codec status data and PCM audio data from the ADC<br>The LM4550 clocks data from this output on the rising edge of BIT_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SYNC      | 10  | I   | AC Link frame marker and Warm Reset<br>This input defines the boundaries of AC Link frames. Each frame lasts 256 periods of BIT_CLK.<br>normal operation SYNC is a 48 kHz positive pulse with a duty cycle of 6.25% (16/256). SYNC is<br>sampled on the rising edge of BIT_CLK and the codec takes the first positive sample of SYNC a<br>defining the start of a new AC Link frame. If a subsequent SYNC pulse occurs within 255 BIT_CL<br>periods of the frame start it will be ignored.<br>SYNC is also used as an active high input to perform an (asynchronous) Warm Reset. Warm Res<br>is used to clear a power down state on the codec AC Link interface.                                                |

| RESET#    | 11  | I   | Cold Reset<br>This active low signal causes a hardware reset which returns the control registers and all intern<br>circuits to their default conditions. RESET# must be used to initialize the LM4550 after Power C<br>when the supplies have stabilized. Cold Reset also clears the codec from both ATE and Vendo<br>test modes. In addition, while active, it switches the PC_BEEP mono input directly to both channe<br>of the LINE_OUT stereo output.                                                                                                                                                                                                                                                       |

| Name                 | Pin      | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID0#                 | 45       | 1   | Codec Identity<br>ID1# and ID0# determine the Codec Identity for multiple codec use. The Codec Identity configures<br>the codec in either Primary or one of three Secondary Codec modes. These Identity pins are of<br>inverted polarity relative to the Codec Identity bits ID1, ID0 (bits D15, D14) in the read-only<br>Extended Audio ID register, 28h. If the ID0# pin (pin 45) is connected to ground then the ID0 bit<br>(D14, reg 28h) will be set to "1". Similarly, connection to DV <sub>DD</sub> will set the ID0 bit to "0". If left oper<br>(NC), ID0# is pulled high by an internal pull-up resistor. The Codec Identity bits are also used in<br>the Chain-In Control register, 74h. See the register description and the CIN pin description for<br>details.                                                                                                                                                                                                            |

| ID1#                 | 46       | I   | Codec Identity<br>ID1# and ID0# determine the codec address for multiple codec use. The Codec Identity configure<br>the codec in either Primary or one of three Secondary Codec modes. These Identity pins are of<br>inverted polarity relative to the Codec Identity bits ID1, ID0 (bits D15, D14) in the read-only<br>Extended Audio ID register, 28h. If the ID1# pin (pin 46) is connected to ground then the ID1 bit<br>(D15, reg 28h) will be set to "1". Similarly, connection to DV <sub>DD</sub> will set the ID1 bit to "0". If left oper<br>(NC), ID1# is pulled high by an internal pull-up resistor. The Codec Identity bits are also used in<br>the Chain-In Control register, 74h. See the register description and the CIN pin description for<br>details.                                                                                                                                                                                                              |

| EAPD                 | 47       | 0   | External Amplifier Power Down control signal.<br>This output is set by the EAPD bit (bit D15) in the Powerdown Control/Status register, 26h. As wit<br>the other logic outputs, the output voltage is set by DV <sub>DD</sub> . This pin is intended to be connected to<br>the shutdown pin on an external power amplifier. For normal operation the default value of EAPD=<br>will enable the external amplifier allowing an input on PC_BEEP to be heard during Cold Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CIN                  | CIN 48 I |     | Chain In<br>The codec can be instructed to disconnect its own SDATA_IN signal and instead pass the signal<br>on CIN through to the SDATA_IN output pin. This is achieved by changing the value of the two<br>LSBs of the Chain-In Control register (74h) so that they differ from the Codec Identity bits ID1, ID0<br>Those two LSBs default to the value of the Codec Identity bits following Cold Reset thereby<br>disabling the Chain In feature. Chain In can also be disabled by reading the Codec Identity from<br>the Extended Audio ID register (26h) and writing the value back into register 74h LSBs. The Code<br>Identity bits are determined by the input pins ID1#, ID0#.<br>CIN can be left open (NC) provided that the chain feature is disabled. When the chain feature is<br>used, CIN should always be driven. Either connect the SDATA_IN pin from another codec or els<br>ground CIN to prevent the possibility of floating the SDATA_IN signal at the controller. |

|                      |          | 2   | POWER SUPPLIES AND REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Name                 | Pin      | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AV <sub>DD</sub>     | 25       |     | Analog supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AV <sub>SS</sub>     | 26       |     | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DV <sub>DD1</sub>    | 1        |     | Digital supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $DV_{DD2}$           | 9        |     | Digital supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $DV_{SS1}$           | 4        |     | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $DV_{SS2}$           | 7        | I   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>REF</sub>     | 27       | 0   | Nominal 2.2 V internal reference<br>Not intended to sink or source current. Use short traces to bypass (3.3 $\mu$ F, 0.1 $\mu$ F) this pin to<br>maximize codec performance. This pin must be tied to AV <sub>DD</sub> with a 10 k $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>REF_OUT</sub> | 28       | 0   | Nominal 2.2 V reference output<br>Can source up to 5 mA of current and can be used to bias a microphone.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                                      |     | 3D SOUND AND NO-CONNECTS (NC)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Pin                                  | 1/0 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3DP, 3DN | 33,34                                | 0   | These pins are used to complete the National 3D Sound stereo enhancement circuit. Connect a $0.022 \ \mu\text{F}$ capacitor between pins 3DP and 3DN. National 3D Sound can be turned on and off via the 3D bit (bit D13) in the General Purpose register, 20h. National 3D Sound uses a fixed-depth type stereo enhancement circuit hence the 3D Control register, 22h is read-only and is not programmable. If National 3D Sound is not needed, these pins should be left open (NC). |

| NC       | 29, 30<br>31, 32<br>38, 42<br>43, 44 | NC  | These pins are not used and should be left open (NC).<br>For second source applications these pins may be connected to a noise-free supply or ground ( <i>e.g.</i> $AV_{DD}$ or $AV_{SS}$ ), either directly or through a capacitor.                                                                                                                                                                                                                                                   |

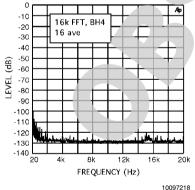

### **Typical Performance Characteristics**

| HEG         Mane         D1         D1 <thd< th=""><th></th><th>M45</th><th>LM4550 Register Map</th><th>de</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></thd<>                                                                                                      |          | M45 | LM4550 Register Map | de   |      |      |      |      |      |      |     |      |      |     |     |     |     |     |     |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|---------------------|------|------|------|------|------|------|------|-----|------|------|-----|-----|-----|-----|-----|-----|---------|

| 000         Final state volume         X         0         0         1         0         1         0         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                         |          | REG |                     | D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8  | D7   | D6   | D5  | D4  | D3  | D2  | D1  | DO  | Default |

| QCD         Mester Volume         Mue         X         Mud         Mul         Mul <th< td=""><td></td><td>400</td><td></td><td>×</td><td>0</td><td>0</td><td>0</td><td>-</td><td>-</td><td>0</td><td>-</td><td>0</td><td>-</td><td>0</td><td>-</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0D50h</td></th<>                                                          |          | 400 |                     | ×    | 0    | 0    | 0    | -    | -    | 0    | -   | 0    | -    | 0   | -   | 0   | 0   | 0   | 0   | 0D50h   |

| Qieb         Image         Miss         Miss <t< td=""><td>မက</td><td></td><td></td><td>Mute</td><td>×</td><td>×</td><td>ML4</td><td>ML3</td><td>ML2</td><td>ML1</td><td>MLO</td><td>×</td><td>×</td><td>×</td><td>MR4</td><td>MR3</td><td>MR2</td><td>MR1</td><td>MRO</td><td>8000h</td></t<> | မက       |     |                     | Mute | ×    | ×    | ML4  | ML3  | ML2  | ML1  | MLO | ×    | ×    | ×   | MR4 | MR3 | MR2 | MR1 | MRO | 8000h   |

| Q6h         Mono Volume         Mut         X         X         X         X         X         X         X         X         Mut         Mut         Mut         Mut         Mut         Mut         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X<                                                                                                                                                                                                                                                                                                                                                                 | njo/     |     |                     | Mute | ×    | ×    | ML4  | ML3  | ML2  | ML1  | MLO | ×    | ×    | ×   | MR4 | MR3 | MR2 | MR1 | MR0 | 8000h   |